信号強度 信号強度 |

|

tran, tranif0, tranif1プリミティブ |

抵抗なので、ドレインから出力される信号は、

ソースよりもオームの法則の分だけ、下がった or 上がったものとなります。

これをVerilog HDL的にいうと、ソースよりも信号強度が一つさがる。です。

(詳しくは後ほど)

また、抵抗という特性の違いだけで、

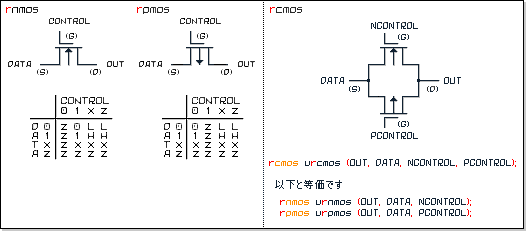

nmosとrnmos。pmosとrpmos。cmosとrcmosの論理は同じです。

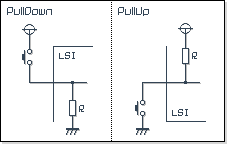

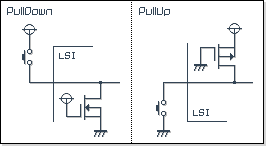

さて、抵抗というと何か思い出しません?

そう、プルアップ抵抗、プルダウン抵抗がありましたよね。

今回は抵抗MOSなので、ゲート端子が余分についていますが、

以下のようにゲート端子を処理すれば、

(要求する特性を満たすかは別として、)

プルアップ抵抗、プルダウン抵抗になります。

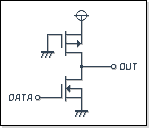

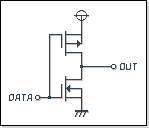

では、次の回路の論理は分かりますか?

ちょっと考えてみてください。

上側のPMOSが抵抗、下側のNMOSがスイッチですので、

・・・そう。これもプルアップですよね。

ただし、スイッチがNMOSなので、

DATA端子に

・Highを入力すると、NMOSがONして、OUT端子はLow出力となり、

・Lowを入力すると、NMOSがOFF(Hi-Z)して、OUT端子はHigh出力となります。

従って、前述のプルアップ抵抗と違って、

入力と出力が反転する。反転の論理となります。

つまり、インバータ回路という訳です。

| DATA | OUT |

|---|---|

| 0 1 | 1 0 |

分かりましたか?

「PMOSのゲートもDATAで制御してやればいいのでは?」

先に言われちゃいましたね。

その通りです。

NMOSとPMOSの両方を使う訳ですから、

その方がCMOSの使い方として適していますね。

「rpmosプリミティブじゃないとだめなのでしょうか?」

(・・・今、言おうと)

simで確かめてみましょう。

信号強度 信号強度 |

|

tran, tranif0, tranif1プリミティブ |